Toshiban kehittämä ohjelmoitavien logiikkapiirien FFSA-rakenne (Fast Fit Structured Array) tarjoaa kustannustehokkaan vaihtoehdon perinteisille FPGA-porttimatriiseille. Se on tarkoitettu erityisesti suunnittelijoille, jotka haluavat nopeasti saada sovellukseensa suorituskykyistä logiikkaa mutta selvitä merkittävästi ASIC-piirejä vähäisemmin suunnittelukuluin jo pienilläkin tuotantovolyymeillä.

| Artikkelin kirjoittaja Patrick Osterloh toimii Toshiba Electronics Europen teknisenä johtajana. |

Kun järjestelmän suunnittelu vaatii integroidun ratkaisun, mutta sopivaa standardipiiriä ei ole tarjolla, ohjelmoitava porttimatriisi FPGA tarjoaa nopeasti ja kohtuullisin kuluin suunniteltavan ratkaisun esimerkiksi protojen tekemiseen tai pienimuotoiseen sarjatuotantoon. Sovelluskohtaisesti asiakkaalle kokonaan räätälöity ASIC-piiri puolestaan soveltuu parhaiten käyttöön silloin, kun vaaditaan hyvin korkean tason integraatiota ja ytimen suorituskykyä sekä vähäistä tehonkulutusta tyypillisesti laitteessa, jota on tarkoitus valmistaa hyvin suuria määriä. Tuotantovolyymin on oltava niin suuri, että alenevasta yksikköhinnasta saatu hyöty kompensoi ASIC-piirin suunnittelun mittavat NRE-kulut (Non-Recurring Engineering). Vahva kysyntä uusien tuotteiden yhä paremmalle suorituskyvylle, edullisemmalle hinnalle ja nopeammille toimitusajoille on saanut suunnittelijat kaipaamaan ratkaisua, joka sijoittuisi näiden kahden vaihtoehdon välimaastoon. Ratkaisun tulisi tarjota sovellukselle huippuluokan suorituskyky ja tuotteen nopea läpimenoaika, mutta merkittävästi alhaisemmin kustannuksin ja tuotantomäärin kuin ASIC.

Itse asiassa tällainen tarve on lisääntynyt jo jonkin aikaa. Aiemmin FPGA-valmistajat ovatkin tarjonneet suunnittelijoille lähestymistavaltaan uusia ratkaisuja kuten minimalistisia FPGA-piirejä tai replikaatiopalveluja, jotka kykenevät siirtämään suunnitelman halvemmalle piirialustalle. Toisaalta ASIC-piirien toimittajatkin ovat tarjonneet uusia tuoteluokkia kuten strukturoituja matriiseja, jotka nopeuttavat piirin kehityssykliä ja alentavat NRE-kustannuksia.

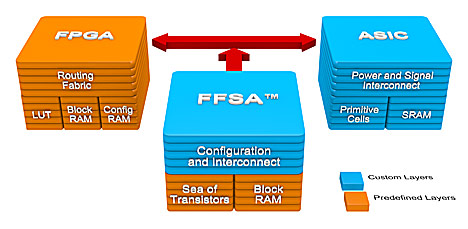

Viime aikoina Toshiba on oivaltanut mahdollisuuden tarjota tähän tarpeeseen erityistä FFSA-piirirakennetta (Fast Fit Structured Array), joka yltää ASIC-piirien kaltaiseen suorituskykyyn mutta paljon alhaisemmin NRE-kuluin verrattuna vastaavaan vakiosoluista koostuvaan ASIC-piiriin. Kuvassa 1 verrataan FPGA-, FFSA- ja ASIC-arkkitehtuureja. Siitä nähdään, kuinka FFSA sijoittuu ominaisuuksiltaan ohjelmoitavien porttimatriisien ja sovelluskohtaisesti asiakkaalle räätälöityjen piirien välimaastoon.

Kuva 1. FFSA-arkkitehtuurissa yhdistyvät FPGA-piirien toteutuksen nopea läpimenoaika sekä ASIC-piirien suorituskyky ja suunnitteluvuo.

FFSA-toteutuksen tärkeimmät edut

FFSA on kustannustehokas myös pienillä tuotantomäärillä ja se voi kilpailla vahvasti FPGA-piirien kanssa jopa kymmenentuhannen kappaleen vuosituotantotasolla. Toshiban valmiudet FFSA- ja ASIC-piireissä tarjoavat yhdessä laajan valikoiman ratkaisuja asiakaspiirien markkinoille. Näin on saatu aikaan luonteva polku siirtyä pehmeästi FPGA-protopiireistä lähes riskittömästi FFSA-toteutukseen pienillä ja keskitason tuotantomäärillä ja lopulta varsinaiseen ASIC-ratkaisuun tai FFSA:n edistyneimpään muotoon siinä vaiheessa, kun on tarve siirtyä lopulliseen suuren volyymin tuotantoon.

FFSA on strukturoitu matriisi, joka muodostuu tasapainoisesta yhdistelmästä logiikkaporttisoluja ja täysin räätälöitävää SRAM-muistia sekä huippunopeita lähetin-vastaanottimia ja ohjelmoitavia I/O-puskureita. Yhdistelmä soveltuu hyvin monentyyppisten asiakkaiden erilaisiin tarpeisiin. Strukturoidun matriisirakenteen ylimmät metallikerrokset on varattu piirin räätälöintiä varten ja alimmat metallikerrokset ovat yhteiset kaikille asiakkaille. Tämän ansiosta osa maskeista voidaan valmistaa jo etukäteen, mikä lyhentää sekä kehitys- että valmistusaikaa ja antaa mahdollisuuden jakaa suurimman osan kokonaiskustannuksista useiden eri asiakassovellusten kesken, jolloin selvitään merkittävästi alhaisemmin NRE-kuluin. Lisäksi kun räätälöinti rajoitetaan vain muutamaan metallikerrokseen, valmistuksen läpimenoaika suunnitelman lopullisesta RTL-datasta ensimmäisten näytepiirien toimituksiin kutistuu tyypillisesti noin kymmeneen viikkoon.

Yhdistelmäkonsepti FFSA+ vielä laajentaa tämän lähestymistavan etuja. Siinä perinteiseen ASIC-piiriin on sisällytetty yksi tai useampia FFSA-lohkoja. Piialusta on valmiiksi täysin räätälöity, mutta sisäiset FFSA-lohkot sallivat ydinlogiikan ja SRAM-muistilohkojen asiakaskohtaisen räätälöinnin hyvin nopeasti vain muutaman metallikerroksen avulla. Näin samasta päätuotteesta voidaan eriyttää erilaisia versioita hyvin nopealla aikataululla ja houkuttelevaan hintaan. Tämä antaa laitevalmistajille mahdollisuuden tuoda markkinoille joko samanaikaisesti tai nopeasti peräkkäin useita yksilöllisiä tuotevariantteja, jotka täyttävät eri markkinasegmenttien tai standardien vaatimukset.

Ei ainoastaan liimalogiikkaa

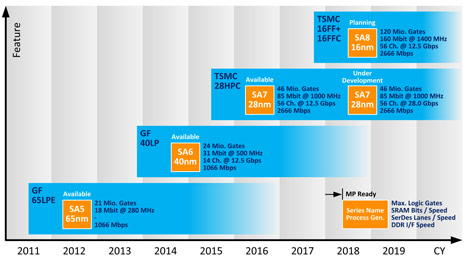

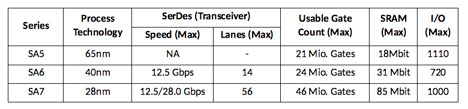

Toshiba jatkaa FFSA-konseptin tukemista kehittämällä uusia IP-lohkoja, jotka tarjoavat vahvan tuen muun muassa muisti- ja verkkolaitteille sekä teollisuuden ja digitaalisen kuvankäsittelyn sovelluksiin. Tärkeimmät toimintalohkot tarjoavat muun muassa metalloinnin avulla konfiguroitavia SRAM-lohkoja, jotka tukevat sekä yksi- että kaksiporttisia SRAM-muisteja, rekistereitä ja ROM-lohkoja. Konsepti sisältää myös monikäyttöisiä I/O-puskureita, jotka tukevat useita eri liitäntästandardeja kuten CMOS, TTL, LVDS, SSTL ja HSTL. Lisäksi tuettuja ovat erittäin nopeat moniprotokollaiset lähetin-vastaanottimet, jotka yltävät 12,5 gigabitin sekuntinopeuksiin linjaa kohti. Ensi vuonna saataville tulevat vieläkin nopeammat lähetin-vastaanottimet, jotka yltävät peräti 28,0 gigabitin sekuntinopeuksiin (Kuva 2). Yhdistämällä saatavilla olevat FFSA-piiriresurssit maineikkaiden IP-toimittajien tuottamiin huippuluokan ohjainlohkoihin, Toshiba tarjoaa FFSA-asiakkailleen käyttövalmiita IP-alijärjestelmiä. Näihin kuuluvat DDR-muistit, PCIe- ja Ethernet-väyläratkaisut sekä eri standardien mukaiset huippunopeat liitännät.

Kuva 2. FFSA-konseptin ominaisuudet ja kehityssuunnitelman aikataulu.

Kuva 3. FFSA-konseptissa on hyödynnetty puolijohdeprosessin kehitysaskelten tuomia parannuksia piirien toimintanopeuksissa ja pakkaustiheydessä.

FFSA-toteutus ei tarjoa ainoastaan alhaisempia kustannuksia, vaan myös noin nelinkertaista logiikan tiheyttä FPGA-toteutukseen verrattunua. Tämän ansiosta suunnittelijat voivat toteuttaa useita FPGA-piirejä vaativan suunnitelman yhdellä FFSA-piirillä. Lisäksi FFSA-piirin tehohäviö on tyypillisesti alle kolmasosa toiminnaltaan vastaavasta FPGA-toteutuksesta. Näin suunnittelijat voivat käyttää laitteen teholähteessä hinnaltaan edullisempia komponentteja sekä yksinkertaistaa laitteen lämpösuunnittelua ja jäähdytysratkaisuja. Tämän ansiosta on mahdollista päästä merkittäviin lisäsäästöihin koko toteutuksen materiaalikuluissa (BOM).

Protoja vaivattomasti

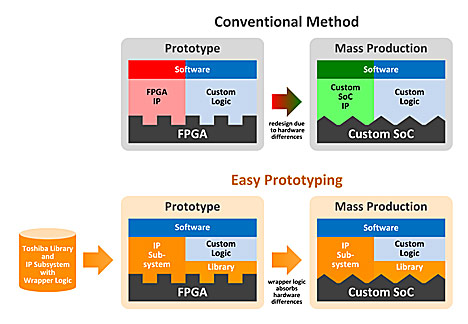

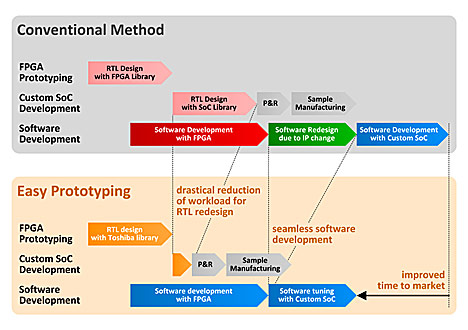

Toshiba on laatinut suunnittelijoita varten helpon kasvupolun FPGA:sta FFSA-toteutukseen, jota se tarjoaa nimellä Easy Prototyping. Kuva 4 esittää reaalimaailman esimerkin siitä, miten FPGA-prototyypin tuottaminen ja halutun FFSA-toteutuksen kehittäminen voidaan toteuttaa samanaikaisesti.

Asiakkaat voivat käyttää alijärjestelminä samoja IP-lohkoja, joita Toshiba tarjoaa sekä FPGA-protopiirejä että FFSA-toteutusta varten. Lisäksi kun asiakkaat käyttävät toteutuksessa alijärjestelminä yhtiön IP-kirjaston lohkoja, joiden ympäryslogiikka on tarkoitettu FPGA-protoja varten, tarve ylläpitää rinnakkain kahta eri RTL-koodiversiota voidaan eliminoida. Näin voidaan säästää arvokkaita suunnitteluresursseja. Käyttämällä samoja IP-alijärjestelmiä ja RTL-koodiversioita sekä FPGA- että FFSA-toteutukseen voidaan myös ohjelmistonkehitys aloittaa jo hyvin varhaisessa vaiheessa. FPGA-protoalustalle suunniteltu alatason ohjauskoodi voidaan saumattomasti siirtää FFSA-alustalle heti, kun ensimmäiset piinäytteet ovat saatavilla. Tämän ansiosta asiakkaat voivat saada merkittävää kilpailuetua lopputuotteen tuomisessa markkinoille mahdollisimman nopeasti. Vastaava Easy Prototyping -konsepti on tarjolla myös ASIC-piirien kehitykseen.

Kuva 4a.

Kuva 4b. FPGA-prototyyppi ja vastaava FFSA-toteutus voidaan suunnitella samanaikaisesti.

Traficom jatkaa varoittelua tietojenkalastelu- eli phishing-sähköposteista. Huijauksia on viime aikoina tehty myös .fi-päätteisillä sivustoilla esimerkiksi Patentti- ja rekisterihallituksen, positiivisen luottotietorekisterin sekä Osuuspankin nimissä.

Traficom jatkaa varoittelua tietojenkalastelu- eli phishing-sähköposteista. Huijauksia on viime aikoina tehty myös .fi-päätteisillä sivustoilla esimerkiksi Patentti- ja rekisterihallituksen, positiivisen luottotietorekisterin sekä Osuuspankin nimissä.

Älypuhelimissa on jatkuva tarve nopeammalle tallennukselle. Tärkeä osa tätä yhtälöä on tallennusstandardi. Kioxia sanoo nyt aloittaneensa uusien flash-piiriensä näytetoimtiukset. ne tukevat uusinta UFS- eli Universal Flash Storage -standardin versiota 4.0.

Älypuhelimissa on jatkuva tarve nopeammalle tallennukselle. Tärkeä osa tätä yhtälöä on tallennusstandardi. Kioxia sanoo nyt aloittaneensa uusien flash-piiriensä näytetoimtiukset. ne tukevat uusinta UFS- eli Universal Flash Storage -standardin versiota 4.0.