FPGA-pohjainen järjestelmä vaatii useita syöttöjännitteitä, joista kullakin on omat vaatimuksensa jännitteen, virran ja kytkentävasteen suhteen. Suunnittelijan on lisäksi kiinnitettävä erityishuomiota syöttölinjojen ryhmittelyyn sekä käynnistyksen ja sammutuksen jaksotuksiin. Aluksi kaikki tehonsyötön vaatimukset kannattaa koota yhteen ja hahmotella puumaiseksi kaavioksi.

| Artikkelin kirjoittaja John Dillon työskentelee Inteliin kuuluvassa Enpirion Power Products -liiketoimintayksikössä. |

Ohjelmoitava porttimatriisi FPGA on nopeasti noussut sulautettujen järjestelmien keskeiseksi rakenneosaksi. Tämä johtuu logiikkamatriisin uudelleenkonfiguroinnin dynaamisuudesta ja valmiudesta rinnakkaisprosessointiin. Näiden ominaisuuksien ansiosta FPGA-piirit tarjoavat ihanteellisen järjestelmäratkaisun lukuisiin sovelluksiin kuten monimutkaisiin neuroverkkoihin ja koneoppimiseen, tietoliikennelaitteisiin sekä ajoneuvon kuljettajan avuksi tarkoitettuihin ADAS-järjestelmiin (Advanced Driver Assistance Systems).

FPGA-piirit ovat yhteensopivia valtavaan joukkoon erilaisia alijärjestelmiä ja tukikomponentteja kuten lähetin-vastaanottimia, PLL-piirejä ja muistilohkoja. Tämä edellyttää, että FPGA-piirille tuodaan useita syöttöjännitteitä, joista kullakin on omat vaatimuksensa jännitteen, virran ja kytkentävasteen suhteen. Esimerkiksi FPGA-ydin todennäköisesti vaatii virtaa kymmeniä ampeereja ja joissakin nykyajan sovelluksissa jopa 90 ampeeria suhteellisen alhaisella, esimerkiksi 0,95 voltin jännitetasolla. Sen sijaan muisti-, logiikka- ja liitäntälohkot vaativat yleensä 1,5 – 3,3 voltin tasoisia syöttöjännitteitä. Lisäksi häiriön- ja kohinansieto ovat tärkeitä näkökohtia teholähteen suunnittelussa. Erityisesti lähetin-vastaanottimille ja vaihelukituille silmukoille (PLL) on syötettävä äärimmäisen puhdasta käyttöjännitettä, jotta aikatason signaalivärinän (jitter) syntyminen ja siirtyminen järjestelmään voidaan estää.

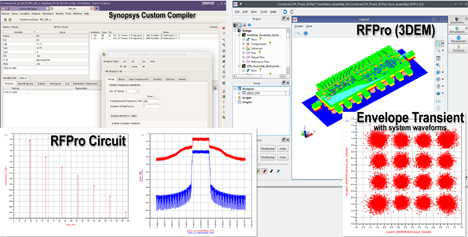

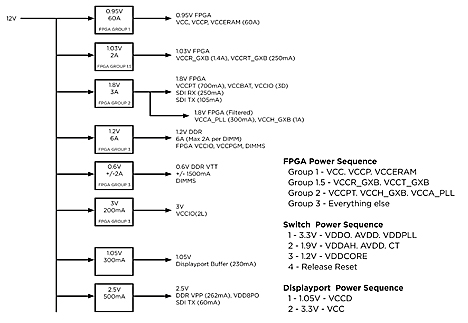

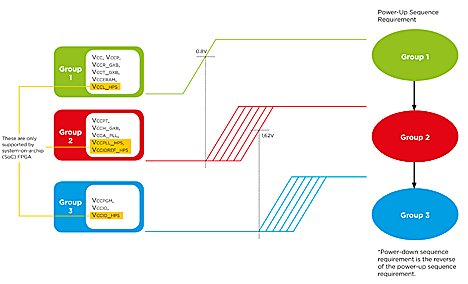

Kuva 1. Varhaisen vaiheen hahmotelma suunniteltavan FPGA-pohjaisen järjestelmän vaatiman teholähteen ominaisuuksista.

Kun FPGA- tai SoC-piiriin perustuvalle järjestelmälle aletaan suunnitella tehonsyöttöä, ensimmäiseksi kannattaa laatia luettelo kaikista tarvittavista syöttöjännitteistä sekä muista kriittisistä parametreista kuten huippuvirroista. Toinen minkä tahansa monimutkaisen järjestelmän keskeinen näkökohta on ryhmitellä ja jaksottaa kunkin tehonsyöttölinjan kytkeytyminen päälle ja pois. Tällainen puumainen hahmotelma on esitetty kuvassa 1. Kaavio kertoo järjestelmän kaikki tehonsyötölle asettamat vaatimukset. Lukuisten erisuuruisten lähtöjännitteiden lisäksi kannattaa kiinnittää huomiota myös tulevalle syöttöjännitteelle asetettaviin vaatimuksiin. Keräämällä ensin kaikki nämä kriteerit samaan kaavioon suunnittelija voi aloittaa teholähteen käytännön suunnittelutyön selkeältä pohjalta.

Nykypäivän sovelluksissa tilaa on yleensä tarjolla rajallisesti, joten suunnittelijan on ensin arvioitava käytettävissä oleva fyysinen tila ja sen jälkeen määritettävä, riittääkö se aiotulle mekaaniselle toteutukselle. Esimerkiksi suunnittelija saattaa haluta järjestelmään lisää tuulettimia jäähdytyksen parantamiseksi. Kyseessä on kuitenkin elementti, jolla on erittäin suuri vaikutus koko teholähteen kuormitukseen ja hyötysuhteeseen.

Teholähteen suunnittelijan täytyy myös arvioida, onko suuremmalle teholähteelle käytettävissä riittävästi pinta-alaa vai onko mahdollista käyttää erillistä teholähdettä tai vaihtoehtoisesti kompaktiin muotoon pakattua tehoregulaattorimoduulia. Erillisratkaisuja on pitkään pidetty kustannustehokkaina, mutta tehomoduulit nähdään yhä useammin parempana vaihtoehtona sekä hinnan, tilankäytön että suorituskyvyn osalta. Esimerkiksi kuvassa 1 esitetyn 0,95V/60A tehonsyötön toteuttaminen erillisratkaisuna käytettävissä olevaan tilaan saattaa yksinkertaisesti olla mahdotonta.

Suunnittelijan tulee myös tarkistaa FPGA-piirin datalehdestä tai sovellusohjeesta liitäntänastoille annetut suositukset ytimelle ja lähetin-vastaanottimille vedettävien syöttölinjojen ominaisuuksista ja sijoittelusta. Tämä informaatio tarjoaa yksityiskohtaiset tiedot syöttöregulaation toleransseista, lämpötilaspesifikaatioista ja kytkentävasteista, joita yksittäisiltä tehonsyöttölinjoilta vaaditaan. On suositeltavaa, että erityistä huomiota kiinnitetään ytimen ja lähetin-vastaanottimien tehonsyötöstä vastaavien regulaattorien valintaan. Pääsyöttöjännitteestä riippuen saatetaan joko tarvita välijännitteellä toimivaa väylämuunninta tai sitten ei.

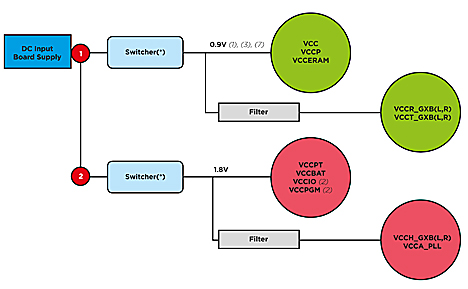

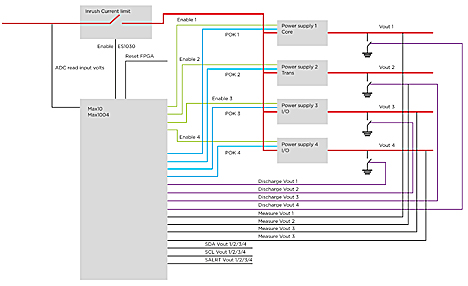

Intel PSG:n kehittämän Arria 10GX -piirin tapauksessa tehonsyöttönastojen kytkentäohje kertoo, kuinka teho tulee piirille syöttää eri vaihtoehdoissa regulaattorien lukumäärästä riippuen. Ytimen syöttöjännite on tällä piirillä 0,9 VDC, jonka sallitaan poikkeavan enintään +/- 30 mV. Kuvassa 2 on 10GX-piirille tarkoitetun teholähteen piirikaavio, kun käytössä on kaksi regulaattoria. Puumaiseen tehonsyöttöhahmotelmaan tarvitaan lisäksi tiedot järjestelmään haluttavista käynnistyksen ja sammutuksen ryhmittelyistä ja jaksotuksista.

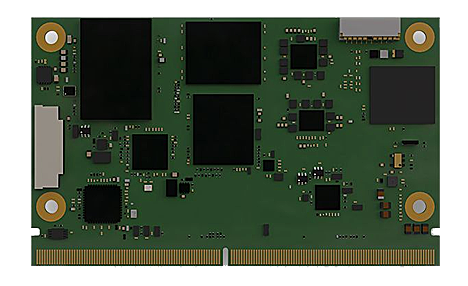

Kuva 2. Esimerkki teholähteestä, joka käyttää kahta regulaattoria (Enpirion).

Tässä esimerkissä tehonsyötön toleranssi on korkeintaan 1,5%, joten teholähteen suunnittelijan tehtävänä on löytää sopivat tehomoduulit tämän saavuttamiseksi. Jotta tehonsyöttöön tarvittavat muutokset voitaisiin tehdä mahdollisimman joustavasti ja hallitusti, regulaattorimoduuleiksi kannattaa valita digitaaliohjauksella varustetut tyypit, joiden avulla tehonsyötön käynnistystä ja sammutusta voidaan täydellisesti ohjata ja valvoa.

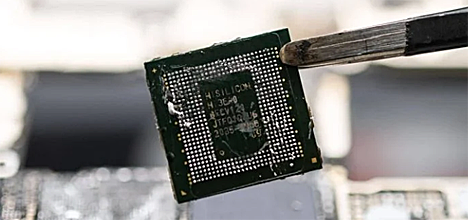

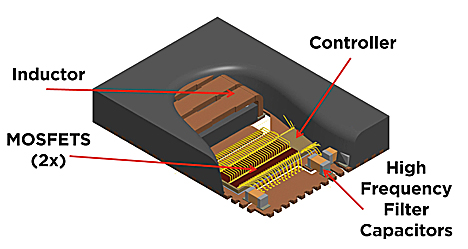

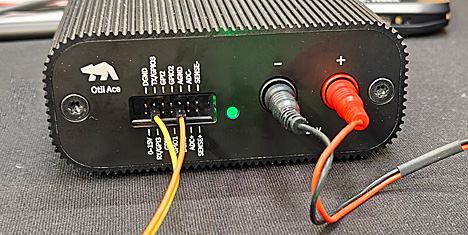

Kuva 3. Enpirion EN63 on hyvä esimerkki regulaattorimoduulista.

Hyvä esimerkki regulaattorimoduuleista on Intelin Altera-ryhmään kuuluvan Enpirion-yhtiön kehittämä EN63xx-sarja (Kuva 3). Korkean hyötysuhteen omaavaan moduulisarjaan kuuluu step-down-tyyppisiä DC-DC-muuntimia, jotka sisältävät myös moduuliin integroidun induktanssin. Sarja tarjoaa erinomaisen yhdistelmän tehotiheyttä ja korkeaa hyötysuhdetta. Esimerkiksi EN6362QI-moduuli on kuuden ampeerin muunnin, johon on integroitu tehokytkimet, induktanssi, hilaohjaus, ohjainpiiri ja kompensointipiirit pieneen 8 x 8 millin QFN-koteloon. Muunnoksen korkean hyötysuhteen ansiosta moduuli voi tuottaa jatkuvaa 6 A virtaa teollisuuskäytön koko lämpötila-alueella.

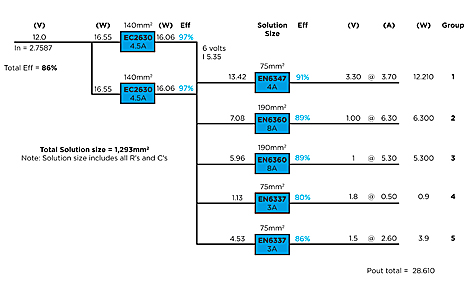

Kun FPGA-piirin ytimen ja lähetin-vastaanottimien regulaattorit on valittu, ’tehonsyöttöpuun’ muut regulaattorit voidaan valita vaadittujen avainparametrien perusteella. Tehovaatimuksista kannattaa hahmotella kuvan 4 kaltainen yhteenveto. Kunkin regulaattorin hyötysuhde tulee määrittää, jotta voidaan päättää, tarvitaanko tehonsyöttöratkaisussa välijännitteellä toimivaa muunninta.

Kuva 4. Esimerkki ’tehonsyöttöpuusta’, johon on koottu kaikki tarvittavat parametrit.

Tehonsyötön suunnittelun tässä vaiheessa voidaan kiinnittää huomiota jaksotusvaatimuksiin. Kuten aiemmin mainittiin, FPGA-piirin sovellusohjeesta saadaan kaikki tarvittavat tiedot järjestelmän käynnistyksen ja sammutuksen ryhmittelyä ja jaksotusta varten. Kuvan 5 esimerkissä tarvitaan kolme erillistä tehonsyöttöryhmää jaksotettavaksi. Siitä nähdään myös jännitteiden kohdat, joissa seuraavat ryhmät voivat aloittaa käynnistyksen.

Kuva 5. Esimerkki käynnistyksen ja sammutuksen jaksottamisesta.

Tehonsyötön sammuttaminen on käynnistykselle vastakkainen prosessi. Suunnittelijan tulee huomioida aika, joka tarvitaan ’tehonsyöttöpuussa’ sijaitsevien kondensaattorien varausten purkamiseen. Purkautumisesta vapautuva teho tulisi poistaa MOSFET-transistorien avulla piirikaavion suurimmista kondensaattoriryhmistä. On tietysti erittäin tärkeää, että tähän käytettävät MOSFET-transistorit kykenevät ongelmitta käsittelemään purkautumisessa siirtyvän tehon ja että ne toimivat parametrien turvallisella alueella, jolloin liiallista lämpöstressiä ei pääse syntymään.

Yhtenä tapana hallita käynnistys- ja sammutusjaksoja voidaan käyttää Intel PSG:n MAX10-piiriä. Kuvassa 6 (alla) on esitetty yksinkertainen piirikaavio tämän toteuttamiseksi neljän tehonsyöttölinjan tapauksessa. MAX10-piiri tarvitsee sammutusprosessia varten ulkopuolisen tehonsyötön vähintään 100 millisekunnin ajaksi sen jälkeen, kun sammutustoiminto on aktivoitu.

Edellä esiteltyjä vaiheita hyödyntäen suunnittelijat voivat laatia tehonsyöttöjärjestelmän rakenteet myös hyvin monimutkaisiin FPGA-pohjaisiin järjestelmiin.

Älypuhelimissa on jatkuva tarve nopeammalle tallennukselle. Tärkeä osa tätä yhtälöä on tallennusstandardi. Kioxia sanoo nyt aloittaneensa uusien flash-piiriensä näytetoimtiukset. ne tukevat uusinta UFS- eli Universal Flash Storage -standardin versiota 4.0.

Älypuhelimissa on jatkuva tarve nopeammalle tallennukselle. Tärkeä osa tätä yhtälöä on tallennusstandardi. Kioxia sanoo nyt aloittaneensa uusien flash-piiriensä näytetoimtiukset. ne tukevat uusinta UFS- eli Universal Flash Storage -standardin versiota 4.0.

Silicon Labs on esitellyt tähän asti energiatehokkaimmat IoT-järjestelmäpiirinsä. XG22E-sarjan sirut on tarkoitettu laitteisiin, jotka saavat tarvitsemansa virran energiankeruulla. Sarjan siruilla on silti radio, joka tukee niin Bluetooth Low Energy-, asiakaskohtaisia 802.15.4- ja alle gigahertsin yhteyksiä.

Silicon Labs on esitellyt tähän asti energiatehokkaimmat IoT-järjestelmäpiirinsä. XG22E-sarjan sirut on tarkoitettu laitteisiin, jotka saavat tarvitsemansa virran energiankeruulla. Sarjan siruilla on silti radio, joka tukee niin Bluetooth Low Energy-, asiakaskohtaisia 802.15.4- ja alle gigahertsin yhteyksiä. Henkilökohtaiseen sähköpostilaatikkoon tipahti perjantaina varsin aidon näköinen kehotus päivittää oman yrityksen yhteystietoja Patentti- ja rekisterihallituksen rekisteriin. Huijaukset muuttuvat yhä laadukkaammiksi, mutta niiden avulla erilaisten tietojen kalastelu jatkuu todennäköisesti niin kauan, kuin toisessa päässä odottaa joku liian innokas hiirellä napsauttelija.

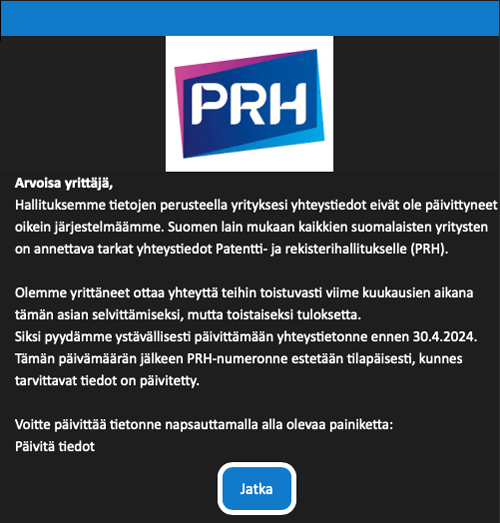

Henkilökohtaiseen sähköpostilaatikkoon tipahti perjantaina varsin aidon näköinen kehotus päivittää oman yrityksen yhteystietoja Patentti- ja rekisterihallituksen rekisteriin. Huijaukset muuttuvat yhä laadukkaammiksi, mutta niiden avulla erilaisten tietojen kalastelu jatkuu todennäköisesti niin kauan, kuin toisessa päässä odottaa joku liian innokas hiirellä napsauttelija.